### **Features**

- Programmable Audio Output for Interfacing with Common Audio DAC

- PCM Format Compatible

- I<sup>2</sup>S Format Compatible

- 8-bit MCU C51 Core-based (F<sub>MAX</sub> = 20 MHz)

- · 2304 Bytes of Internal RAM

- 64K Bytes of Code Memory

- AT89C5132: Flash (100K Write/Erase Cycles)

- 4K Bytes of Boot Flash Memory (AT89C5132)

- ISP: Download from USB (standard) or UART (option)

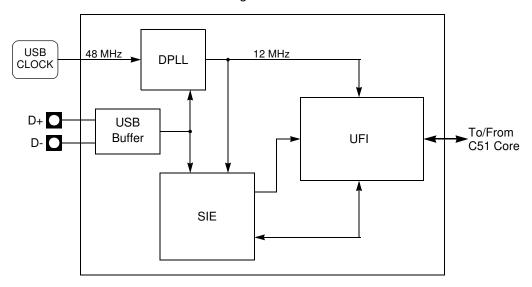

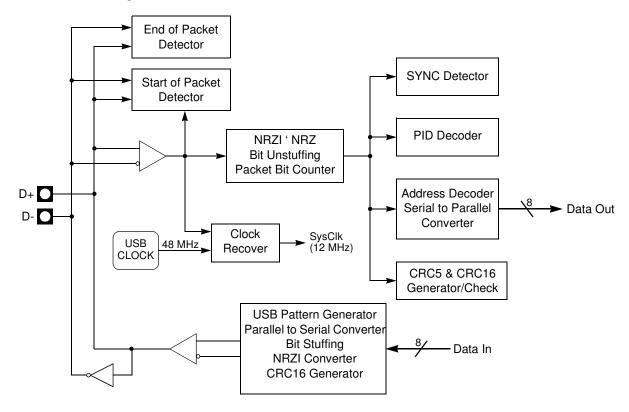

- USB Rev 1.1 Device Controller

- "Full Speed" Data Transmission

- Built-in PLL

- MultiMedia Card<sup>®</sup> Interface Compatibility

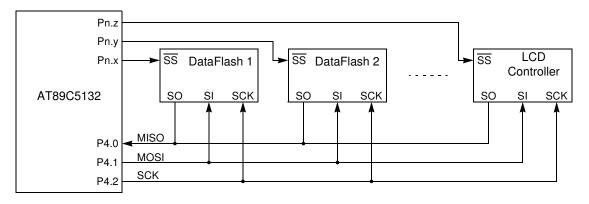

- Atmel DataFlash® SPI Interface Compatibility

- IDE/ATAPI Interface

- · 2 Channels 10-bit ADC, 8 kHz (8 True Bits)

- Battery Voltage Monitoring

- Voice Recording Controlled by Software

- Up to 44 Bits of General-purpose I/Os

- 4-bit Interrupt Keyboard Port for a 4 x n Matrix

- SmartMedia<sup>®</sup> Software Interface

- Two Standard 16-bit Timers/Counters

- · Hardware Watchdog Timer

- Standard Full Duplex UART with Baud Rate Generator

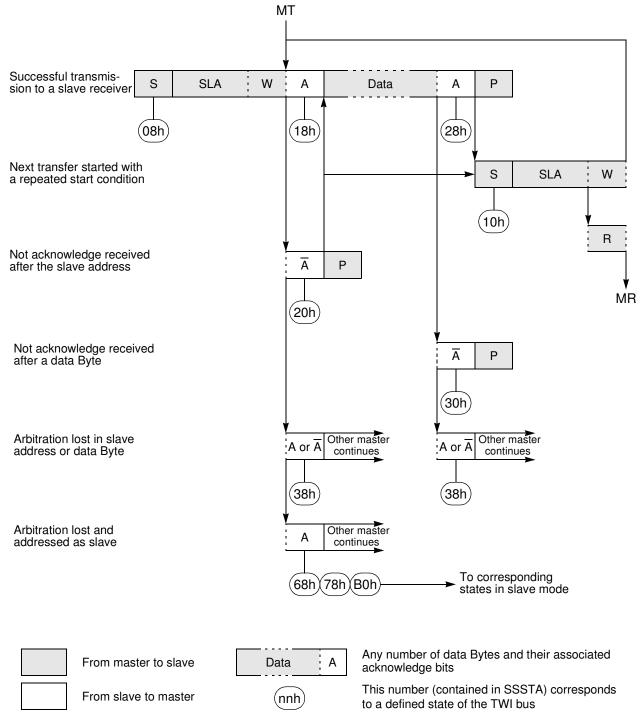

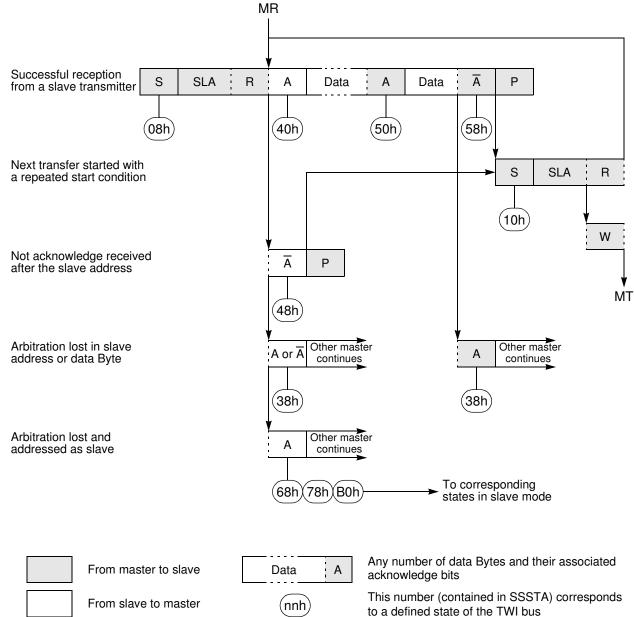

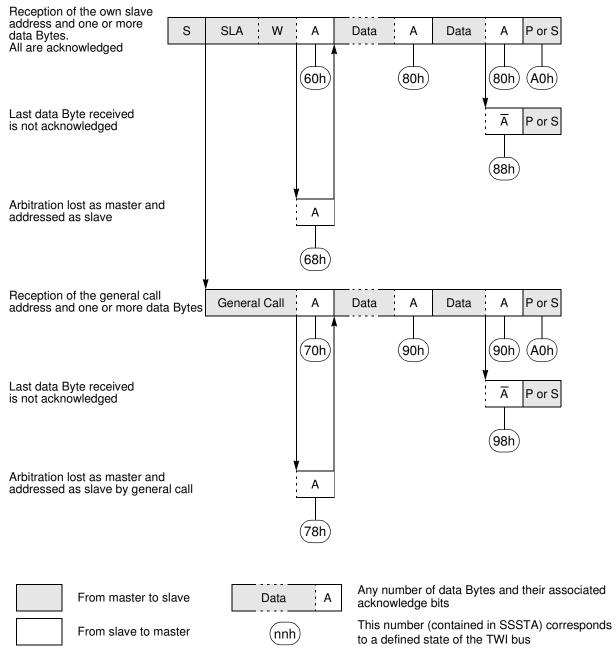

- Two Wire Master and Slave Modes Controller

- SPI Master and Slave Modes Controller

- Power Management

- Power-on Reset

- Software Programmable MCU Clock

- Idle Mode, Power-down Mode

- · Operating Conditions

- 3V, ±10%, 25 mA Typical Operating at 25 °C

- Temperature Range: -40°C to +85°C

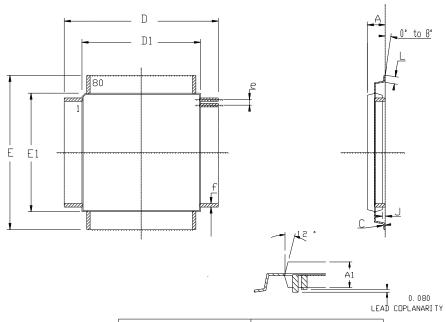

- Packages

- TQFP80, PLCC84 (Development Board Only)

- Dice

# 1. Description

The AT89C5132 is a mass storage device controlling data exchange between various Flash modules, HDD and CD-ROM.

The AT89C5132 includes 64K Bytes of Flash memory and allows In-System Programming through an embedded 4K Bytes of Boot Flash Memory.

The AT89C5132 include 2304 Bytes of RAM memory.

The AT89C5132 provides all the necessary features for man-machine interface including, timers, keyboard port, serial or parallel interface (USB, SPI, IDE), ADC input, I<sup>2</sup>S output, and all external memory interface (NAND or NOR Flash, SmartMedia, MultiMedia, DataFlash cards).

# 2. Typical Applications

- Flash Recorder/Writer

- · PDA, Camera, Mobile Phone

- PC Add-on

# USB Microcontroller with 64K Bytes Flash Memory

AT89C5132

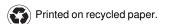

# 3. Block Diagram

Figure 3-1. AT89C5132 Block Diagram

Notes: 1. Alternate function of Port 3

2. Alternate function of Port 4

3. Alternate function of Port 1

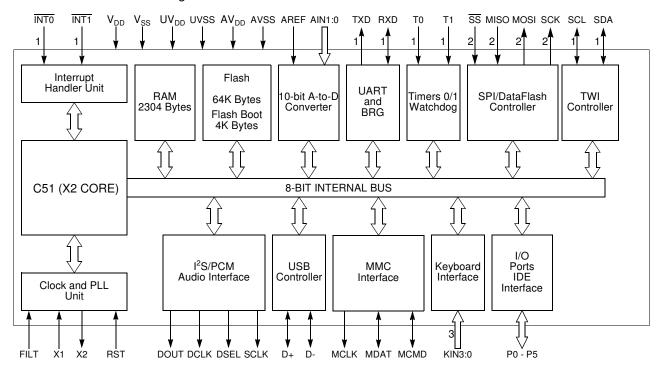

# 4. Pin Description

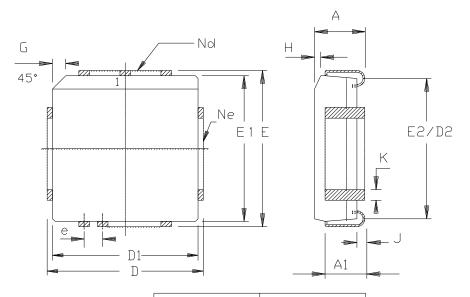

Figure 4-1. AT89C5132 80-pin TQFP Package

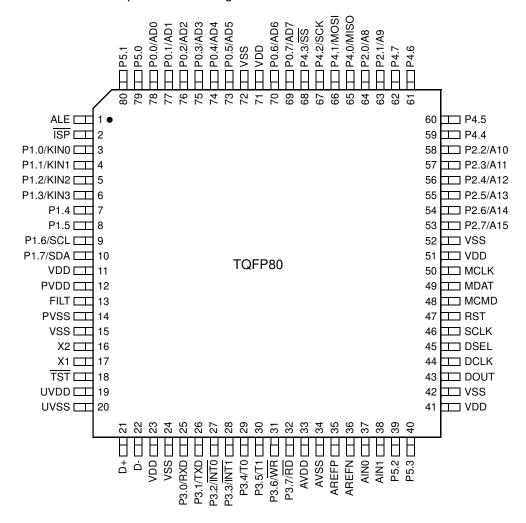

Figure 4-2. AT89C5132 84-pin PLCC (1)

Note: 1. For development board only.

# 4.1 Signals

All the AT89C5132 signals are detailed by functionality in Table 1 to Table 14. **Table 1.** Ports Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                                | Alternate<br>Function |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| P0.7:0         | I/O  | Port 0 P0 is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high impedance inputs. To avoid any parasitic current consumption, floating P0 inputs must be polarized to V <sub>DD</sub> or V <sub>SS</sub> . | AD7:0                 |

| P1.7:0         | I/O  | Port 1 P1 is an 8-bit bidirectional I/O port with internal pull-ups.                                                                                                                                                                                                       | KIN3:0<br>SCL<br>SDA  |

| Signal<br>Name | Туре | Description                                                          | Alternate<br>Function                              |

|----------------|------|----------------------------------------------------------------------|----------------------------------------------------|

| P2.7:0         | I/O  | Port 2 P2 is an 8-bit bidirectional I/O port with internal pull-ups. | A15:8                                              |

| P3.7:0         | I/O  | Port 3 P3 is an 8-bit bidirectional I/O port with internal pull-ups. | RXD<br>TXD<br>INTO<br>INT1<br>T0<br>T1<br>WR<br>RD |

| P4.7:0         | I/O  | Port 4 P4 is an 8-bit bidirectional I/O port with internal pull-ups. | MISO<br>MOSI<br>SCK<br>SS                          |

| P5.3:0         | I/O  | Port 5 P5 is a 4-bit bidirectional I/O port with internal pull-ups.  | -                                                  |

Table 2. Clock Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                    | Alternate<br>Function |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X1             | I    | Input to the on-chip inverting oscillator amplifier  To use the internal oscillator, a crystal/resonator circuit is connected to this pin. If an external oscillator is used, its output is connected to this pin. X1 is the clock source for internal timing. | -                     |

| X2             | 0    | Output of the on-chip inverting oscillator amplifier To use the internal oscillator, a crystal/resonator circuit is connected to this pin. If an external oscillator is used, leave X2 unconnected.                                                            | -                     |

| FILT           | I    | PLL Low Pass Filter input FILT receives the RC network of the PLL low pass filter.                                                                                                                                                                             | -                     |

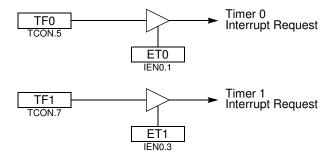

Table 3. Timer 0 and Timer 1 Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                                                                                  | Alternate<br>Function |

|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

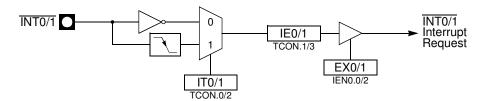

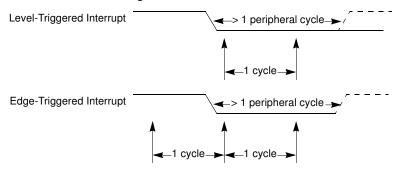

| ĪNTO           | I    | Timer 0 Gate Input INT0 serves as external run control for timer 0, when selected by GATE0 bit in TCON register.  External Interrupt 0 INT0 input sets IE0 in the TCON register. If bit IT0 in this register is set, bit IE0 is set by a falling edge on INT0. If bit IT0 is cleared, bit IE0 is set by a low level on INT0. | P3.2                  |

| ĪNT1           | I    | Timer 1 Gate Input INT1 serves as external run control for timer 1, when selected by GATE1 bit in TCON register.  External Interrupt 1 INT1 input sets IE1 in the TCON register. If bit IT1 in this register is set, bit IE1 is set by a falling edge on INT1. If bit IT1 is cleared, bit IE1 is set by a low level on INT1. | P3.3                  |

| Signal<br>Name | Туре | Description                                                                                                         | Alternate<br>Function |

|----------------|------|---------------------------------------------------------------------------------------------------------------------|-----------------------|

| ТО             | I    | Timer 0 External Clock Input When timer 0 operates as a counter, a falling edge on the T0 pin increments the count. | P3.4                  |

| T1             | I    | Timer 1 External Clock Input When timer 1 operates as a counter, a falling edge on the T1 pin increments the count. | P3.5                  |

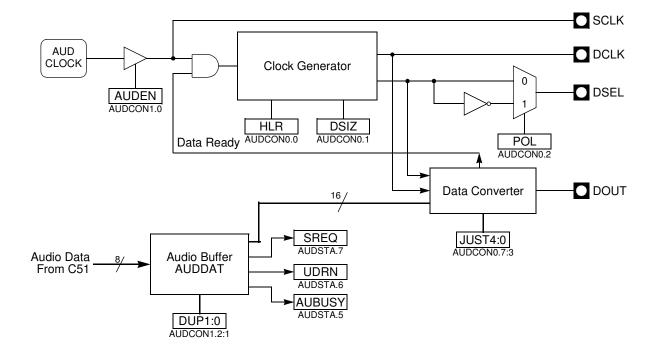

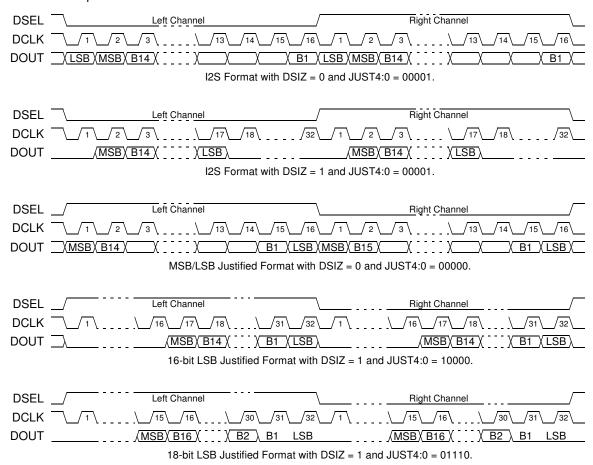

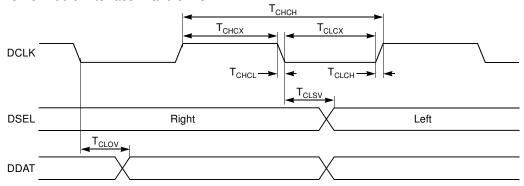

# Table 4. Audio Interface Signal Description

| Signal<br>Name | Туре | Description                                                                                                                            | Alternate<br>Function |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| DCLK           | 0    | DAC Data Bit Clock                                                                                                                     | -                     |

| DOUT           | 0    | DAC Audio Data                                                                                                                         | -                     |

| DSEL           | 0    | DAC Channel Select Signal DSEL is the sample rate clock output.                                                                        | -                     |

| SCLK           | 0    | DAC System Clock SCLK is the oversampling clock synchronized to the digital audio data (DOUT) and the channel selection signal (DSEL). | -                     |

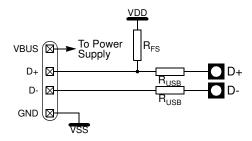

### Table 5. USB Controller Signal Description

| Signal<br>Name | Туре | Description                                                                                                                       | Alternate<br>Function |

|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------|

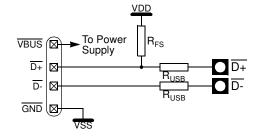

| D+             | I/O  | USB Positive Data Upstream Port This pin requires an external 1.5 K $\Omega$ pull-up to V <sub>DD</sub> for full speed operation. | -                     |

| D-             | I/O  | USB Negative Data Upstream Port                                                                                                   | -                     |

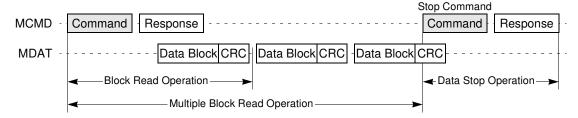

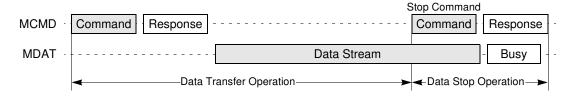

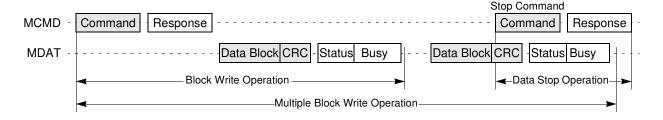

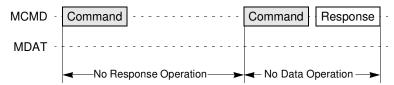

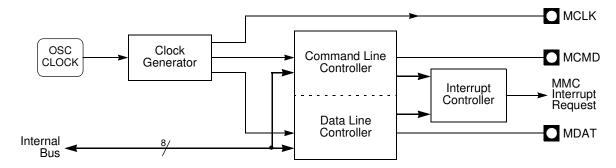

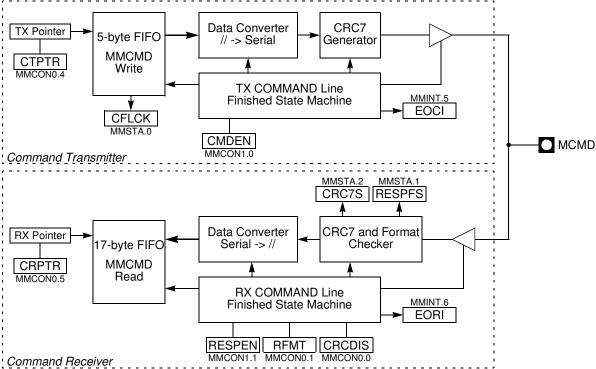

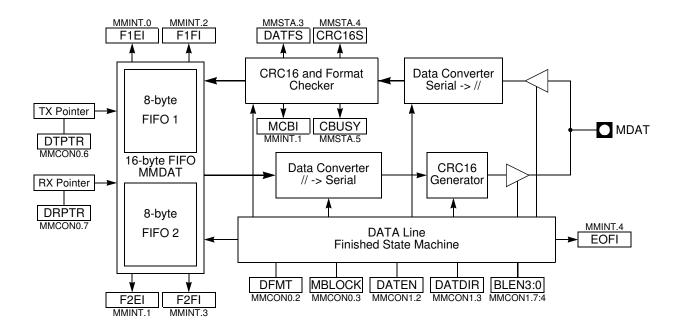

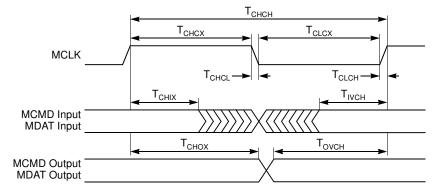

### Table 6. MutiMediaCard Interface Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                     | Alternate<br>Function |

|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| MCLK           | 0    | MMC Clock output Data or command clock transfer.                                                                                                                                                                                | -                     |

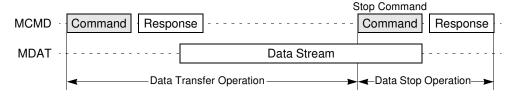

| MCMD           | I/O  | MMC Command line Bidirectional command channel used for card initialization and data transfer commands. To avoid any parasitic current consumption, unused MCMD input must be polarized to V <sub>DD</sub> or V <sub>SS</sub> . | -                     |

| MDAT           | I/O  | $\label{eq:mmc} \begin{array}{l} \textbf{MMC Data line} \\ \text{Bidirectional data channel. To avoid any parasitic current consumption, unused} \\ \text{MDAT input must be polarized to $V_{DD}$ or $V_{SS}$.} \end{array}$   | -                     |

Table 7. UART Signal Description

| Signal<br>Name | Туре | Description                                                                                                              | Alternate<br>Function |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------|-----------------------|

| RXD            | I/O  | Receive Serial Data RXD sends and receives data in serial I/O mode 0 and receives data in serial I/O modes 1, 2 and 3.   | P3.0                  |

| TXD            | 0    | Transmit Serial Data TXD outputs the shift clock in serial I/O mode 0 and transmits data in serial I/O modes 1, 2 and 3. | P3.1                  |

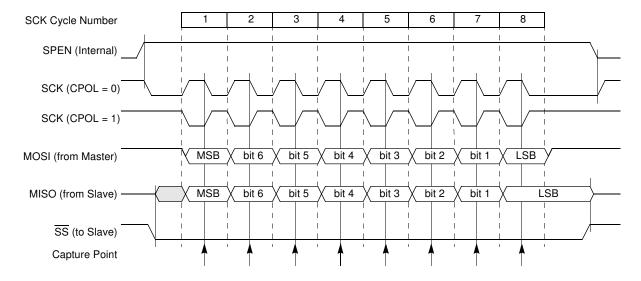

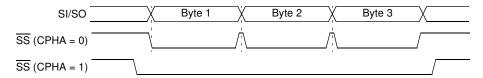

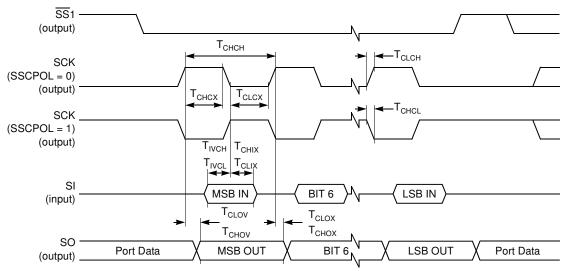

### Table 8. SPI Controller Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                                | Alternate<br>Function |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| MISO           | I/O  | SPI Master Input Slave Output Data Line When in master mode, MISO receives data from the slave peripheral. When in slave mode, MISO outputs data to the master controller. | P4.0                  |

| MOSI           | I/O  | SPI Master Output Slave Input Data Line When in master mode, MOSI outputs data to the slave peripheral. When in slave mode, MOSI receives data from the master controller. | P4.1                  |

| SCK            | I/O  | SPI Clock Line When in master mode, SCK outputs clock to the slave peripheral. When in slave mode, SCK receives clock from the master controller.                          | P4.2                  |

| SS             | I    | SPI Slave Select Line When in controlled slave mode, SS enables the slave mode.                                                                                            | P4.3                  |

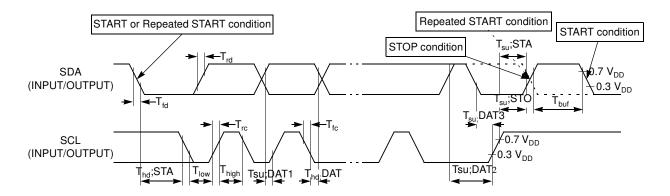

# Table 9. TWI Controller Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                                                         | Alternate<br>Function |

|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| SCL            | I/O  | TWI Serial Clock When TWI controller is in master mode, SCL outputs the serial clock to the slave peripherals. When TWI controller is in slave mode, SCL receives clock from the master controller. | P1.6                  |

| SDA            | I/O  | TWI Serial Data SDA is the bidirectional Two Wire data line.                                                                                                                                        | P1.7                  |

# Table 10. A/D Converter Signal Description

| Signal<br>Name | Туре | Description                                                                       | Alternate<br>Function |

|----------------|------|-----------------------------------------------------------------------------------|-----------------------|

| AIN1:0         | I    | A/D Converter Analog Inputs                                                       | -                     |

| AREFP          | I    | Analog Positive Voltage Reference Input                                           | -                     |

| AREFN          | I    | Analog Negative Voltage Reference Input This pin is internally connected to AVSS. | -                     |

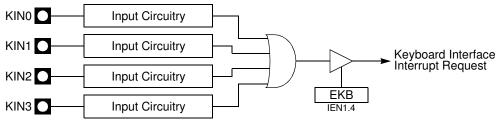

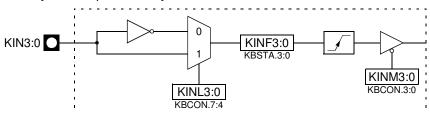

Table 11. Keypad Interface Signal Description

| Signal<br>Name | Туре | Description                                                                                                     | Alternate<br>Function |

|----------------|------|-----------------------------------------------------------------------------------------------------------------|-----------------------|

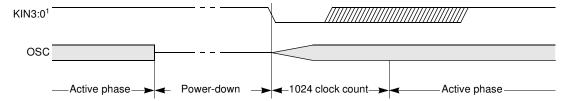

| KIN3:0         | I    | Keypad Input Lines Holding one of these pins high or low for 24 oscillator periods triggers a keypad interrupt. | P1.3:0                |

# Table 12. External Access Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                     | Alternate<br>Function |

|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A15:8          | I/O  | Address Lines Upper address lines for the external bus. Multiplexed higher address and data lines for the IDE interface.                                                                                                        | P2.7:0                |

| AD7:0          | I/O  | Address/Data Lines Multiplexed lower address and data lines for the external memory or the IDE interface.                                                                                                                       | P0.7:0                |

| ALE            | 0    | Address Latch Enable Output ALE signals the start of an external bus cycle and indicates that valid address information is available on lines A7:0. An external latch is used to demultiplex the address from address/data bus. | -                     |

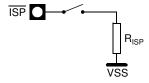

| ĪSP            | I/O  | ISP Enable Input This signal must be held to GND through a pull-down resistor at the falling reset to force execution of the internal bootloader.                                                                               | =                     |

| RD             | 0    | Read Signal Read signal asserted during external data memory read operation.                                                                                                                                                    | P3.7                  |

| WR             | 0    | Write Signal Write signal asserted during external data memory write operation.                                                                                                                                                 | P3.6                  |

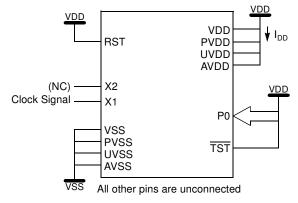

Table 13. System Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Alternate<br>Function |

|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

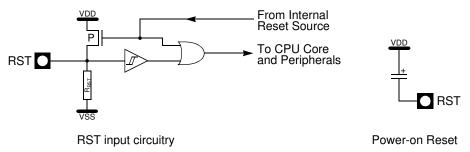

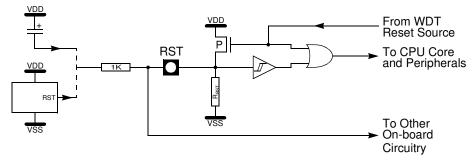

| RST            | I    | Reset Input Holding this pin high for 64 oscillator periods while the oscillator is running resets the device. The Port pins are driven to their reset conditions when a voltage lower than $V_{IL}$ is applied, whether or not the oscillator is running. This pin has an internal pull-down resistor which allows the device to be reset by connecting a capacitor between this pin and $V_{DD}$ . Asserting RST when the chip is in Idle mode or Power-Down mode returns the chip to normal operation. | -                     |

| TST            | I    | Test Input Test mode entry signal. This pin must be set to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                              | -                     |

Table 14. Power Signal Description

| Signal<br>Name | Туре | Description                                                      | Alternate<br>Function |

|----------------|------|------------------------------------------------------------------|-----------------------|

| VDD            | PWR  | Digital Supply Voltage Connect these pins to +3V supply voltage. | -                     |

| VSS            | GND  | Circuit Ground Connect these pins to ground.                     | -                     |

| AVDD           | PWR  | Analog Supply Voltage Connect this pin to +3V supply voltage.    | -                     |

| AVSS           | GND  | Analog Ground Connect this pin to ground.                        | -                     |

| PVDD           | PWR  | PLL Supply voltage Connect this pin to +3V supply voltage.       | -                     |

| PVSS           | GND  | PLL Circuit Ground Connect this pin to ground.                   | -                     |

| UVDD           | PWR  | USB Supply Voltage<br>Connect this pin to +3V supply voltage.    | -                     |

| UVSS           | GND  | USB Ground Connect this pin to ground.                           | -                     |

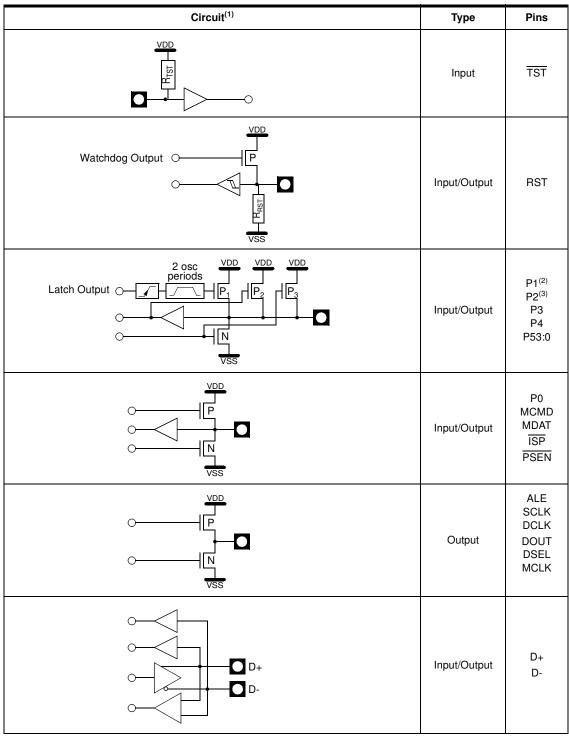

### 4.2 Internal Pin Structure

Table 15. Detailed Internal Pin Structure

Notes:

- 1. For information on resistors value, input/output levels, and drive capability, refer to the Section "DC Characteristics", page 183.

- 2. When the Two Wire controller is enabled, P<sub>1</sub>, P<sub>2</sub>, and P<sub>3</sub> transistors are disabled allowing pseudo open-drain structure.

- 3. In Port 2, P<sub>1</sub> transistor is continuously driven when outputting a high level bit address (A15:8).

# 5. Address Spaces

The AT8xC5132 derivatives implement four different address spaces:

- Program/Code Memory

- Boot Memory

- Data Memory

- Special Function Registers (SFRs)

#### 5.0.1 Code Memory

The AT89C5132 implements 64K Bytes of on-chip program/code memory in Flash technology.

The Flash memory increases ROM functionality by enabling in-circuit electrical erasure and programming. Thanks to the internal charge pump, the high voltage needed for programming or erasing Flash cells is generated on-chip using the standard VDD voltage. Thus, the AT89C5132 can be programmed using only one voltage and allows in application software programming commonly known as IAP. Hardware programming mode is also available using specific programming tools.

#### 5.0.2 Boot Memory

The AT89C5132 implements 4K Bytes of on-chip boot memory provided in Flash technology. This boot memory is delivered programmed with a standard bootloader software allowing in system programming commonly known as ISP. It also contains some Application Programming Interfaces routines commonly known as API allowing user to develop his own bootloader.

#### 5.0.3 Data Memory

The AT89C5132 derivatives implement 2304 bytes of on-chip data RAM. This memory is divided in two separate areas:

- 256 bytes of on-chip RAM memory (standard C51 memory).

- 2048 bytes of on-chip expanded RAM memory (ERAM accessible via MOVX instructions).

### 6. Clock Controller

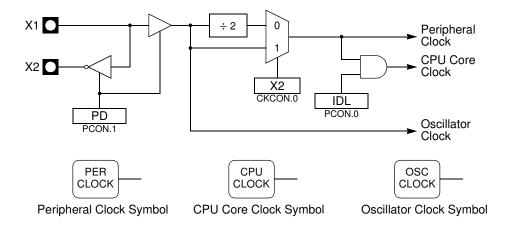

The AT89C5132 clock controller is based on an on-chip oscillator feeding an on-chip Phase Lock Loop (PLL). All internal clocks to the peripherals and CPU core are generated by this controller.

### 6.1 Oscillator

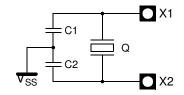

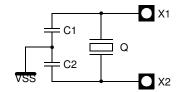

The AT89C5132 X1 and X2 pins are the input and the output of a single-stage on-chip inverter (see Figure 6-1) that can be configured with off-chip components such as a Pierce oscillator (see Figure 6-2). Value of capacitors and crystal characteristics are detailed in the Section "DC Characteristics".

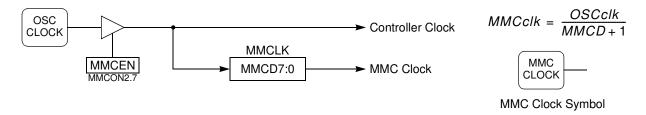

The oscillator outputs three different clocks: a clock for the PLL, a clock for the CPU core, and a clock for the peripherals as shown in Figure 6-1. These clocks are either enabled or disabled, depending on the power reduction mode as detailed in the section "Power Management" on page 44. The peripheral clock is used to generate the Timer 0, Timer 1, MMC, ADC, SPI, and Port sampling clocks.

Figure 6-1. Oscillator Block Diagram and Symbol

Figure 6-2. Crystal Connection

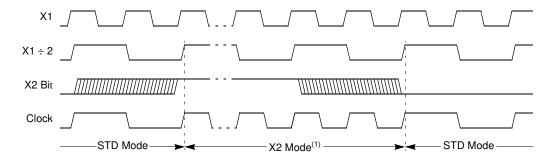

#### 6.2 X2 Feature

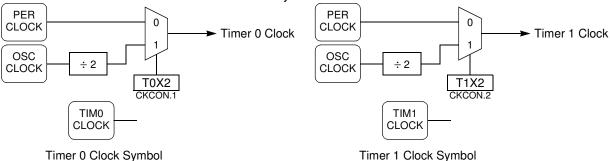

Unlike standard C51 products that require 12 oscillator clock periods per machine cycle, the AT89C5132 needs only 6 oscillator clock periods per machine cycle. This feature called the "X2 feature" can be enabled using the X2 bit<sup>(1)</sup> in CKCON (see Table 1) and allows the AT89C5132 to operate in 6 or 12 oscillator clock periods per machine cycle. As shown in Figure 6-1, both CPU and peripheral clocks are affected by this feature. Figure 6-3 shows the X2 mode switching waveforms. After reset, the standard mode is activated. In standard mode, the CPU and periph-

eral clock frequency is the oscillator frequency divided by 2 while in X2 mode, it is the oscillator frequency.

Note:

The X2 bit reset value depends on the X2B bit in the Hardware Security Byte (see Table 12 on page 24). Using the AT89C5132 (Flash Version) the system can boot either in standard or X2 mode depending on the X2B value. Using AT83C51SND1C (ROM Version) the system always boots in standard mode. X2B bit can be changed to X2 mode later by software.

Figure 6-3. Mode Switching Waveforms

Note: In order to prevent any incorrect operation while operating in X2 mode, the user must be aware that all peripherals using clock frequency as time reference (timers...) will have their time reference divided by two. For example, a free running timer generating an interrupt every 20 ms will then generate an interrupt every 10 ms.

#### 6.3 PLL

### 6.3.1 PLL Description

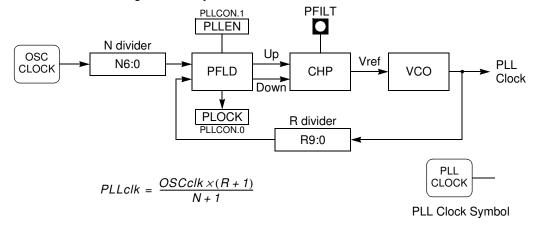

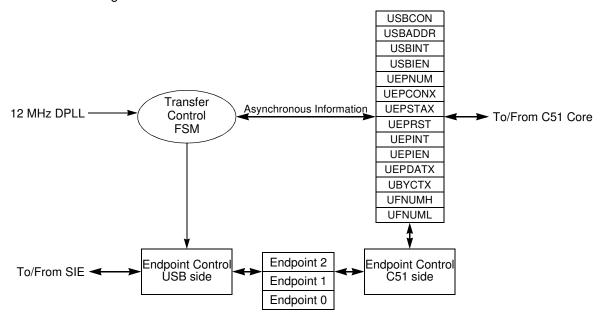

The AT89C5132 PLL is used to generate internal high frequency clock (the PLL Clock) synchronized with an external low-frequency (the Oscillator Clock). The PLL clock provides the audio interface, and the USB interface clocks. Figure 6-4 shows the internal structure of the PLL.

The PFLD block is the Phase Frequency Comparator and Lock Detector. This block makes the comparison between the reference clock coming from the N divider and the reverse clock coming from the R divider and generates some pulses on the Up or Down signal depending on the edge position of the reverse clock. The PLLEN bit in PLLCON register is used to enable the clock generation. When the PLL is locked, the bit PLOCK in PLLCON register (see Table 3) is

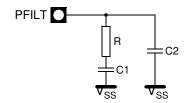

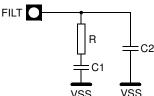

The CHP block is the Charge Pump that generates the voltage reference for the VCO by injecting or extracting charges from the external filter connected on PFILT pin (see Figure 6-5). Value of the filter components are detailed in the Section "DC Characteristics".

The VCO block is the Voltage Controlled Oscillator controlled by the voltage  $V_{ref}$  produced by the charge pump. It generates a square wave signal: the PLL clock.

Figure 6-4. PLL Block Diagram and Symbol

Figure 6-5. PLL Filter Connection

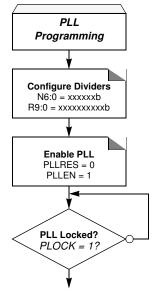

#### 6.3.2 PLL Programming

The PLL is programmed using the flow shown in Figure 6-6. As soon as clock generation is enabled, the user must wait until the lock indicator is set to ensure the clock output is stable. The PLL clock frequency will depend on the audio interface clock frequencies.

Figure 6-6. PLL Programming Flow

### 6.4 Registers

14

Table 1. CKCON Register

# CKCON (S:8Fh) - Clock Control Register

| 7          | 6               | 5                                                                                                                                                                                                | 4                                                                                                                                                                                                 | 3                                                      | 2                | 1      | 0          |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------|--------|------------|

| TWIX2      | WDX2            | -                                                                                                                                                                                                | SIX2                                                                                                                                                                                              | -                                                      | T1X2             | T0X2   | X2         |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                                                                      |                                                                                                                                                                                                   |                                                        |                  |        |            |

| 7          | TWIX2           | Set to select t                                                                                                                                                                                  |                                                                                                                                                                                                   | t<br>ock divided by 2<br>I clock as TWI c              |                  |        | endent).   |

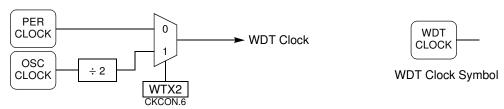

| 6          | WDX2            | Set to select to                                                                                                                                                                                 | Watchdog Clock Control Bit Set to select the oscillator clock divided by 2 as watchdog clock input (X2 independent). Clear to select the peripheral clock as watchdog clock input (X2 dependent). |                                                        |                  |        |            |

| 5          | -               | Reserved<br>The value rea                                                                                                                                                                        | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                                                                                      |                                                        |                  |        |            |

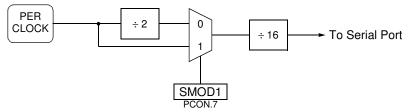

| 4          | SIX2            | Set to select t                                                                                                                                                                                  | he oscillator clo                                                                                                                                                                                 | ode 0 and 2) Co<br>ock divided by 2<br>I clock as UAR1 | as UART cloc     |        | ependent). |

| 3          | -               | Reserved<br>The value rea                                                                                                                                                                        | d from this bit i                                                                                                                                                                                 | s indeterminate                                        | . Do not set thi | s bit. |            |

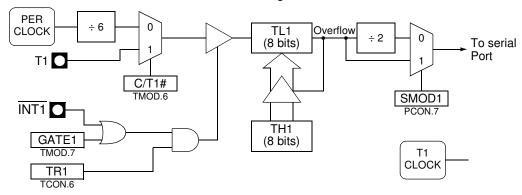

| 2          | T1X2            | Set to select t                                                                                                                                                                                  | Timer 1 Clock Control Bit Set to select the oscillator clock divided by two as Timer 1 clock input (X2 independent). Clear to select the peripheral clock as Timer 1 clock input (X2 dependent).  |                                                        |                  |        |            |

| 1          | T0X2            | Timer 0 Clock Control Bit Set to select the oscillator clock divided by two as timer 0 clock input (X2 independent). Clear to select the peripheral clock as timer 0 clock input (X2 dependent). |                                                                                                                                                                                                   |                                                        |                  |        |            |

| 0          | X2              |                                                                                                                                                                                                  | t 12 clock perio                                                                                                                                                                                  | ods per machine<br>per machine cy                      |                  |        |            |

Reset Value = 0000 000Xb

Table 2. PLLNDIV Register

PLLNDIV (S:EEh) – PLL N Divider Register

| 7          | 6               | 5                               | 4                  | 3              | 2                 | 1  | 0  |

|------------|-----------------|---------------------------------|--------------------|----------------|-------------------|----|----|

| -          | N6              | N5                              | N4                 | N3             | N2                | N1 | N0 |

| Bit Number | Bit<br>Mnemonic | Description                     |                    |                |                   |    |    |

| 7          | -               | Reserved<br>The value read      | d from this bit is | s always 0. Do | not set this bit. |    |    |

| 6-0        | N6:0            | PLL N Divide<br>7-bit N divider |                    |                |                   |    |    |

Reset Value = 0000 0000b

Table 3. PLLCON Register

PLLCON (S:E9h) - PLL Control Register

| 7          | 6               | 5                                                               | 4                                                                                                    | 3               | 2                | 1     | 0     |

|------------|-----------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------|------------------|-------|-------|

| R1         | R0              | -                                                               | -                                                                                                    | PLLRES          | -                | PLLEN | PLOCK |

| Bit Number | Bit<br>Mnemonic | Description                                                     |                                                                                                      |                 |                  |       |       |

| 7 - 6      | R1:0            |                                                                 | <b>gnificant Bits</b> I<br>0-bit R divider.                                                          |                 |                  |       |       |

| 5 - 4      | -               | Reserved<br>The values rea                                      | Reserved The values read from these Bits are always 0. Do not set these Bits.                        |                 |                  |       |       |

| 3          | PLLRES          | Set this bit to                                                 | PLL Reset Bit Set this bit to reset the PLL. Clear this bit to free the PLL and allow enabling.      |                 |                  |       |       |

| 2          | -               | Reserved<br>The values rea                                      | ad from this bit                                                                                     | is always 0. Do | not set this bit |       |       |

| 1          | PLLEN           | PLL Enable Bit Set to enable the PLL. Clear to disable the PLL. |                                                                                                      |                 |                  |       |       |

| 0          | PLOCK           | Set by hardwa                                                   | PLL Lock Indicator<br>Set by hardware when PLL is locked.<br>Clear by hardware when PLL is unlocked. |                 |                  |       |       |

Reset Value = 0000 1000b

Table 4. PLLRDIV Register

PLLRDIV (S:EFh) – PLL R Divider Register

| 7          | 6               | 5                            | 4                                          | 3  | 2  | 1  | 0  |

|------------|-----------------|------------------------------|--------------------------------------------|----|----|----|----|

| R9         | R8              | R7                           | R6                                         | R5 | R4 | R3 | R2 |

| Bit Number | Bit<br>Mnemonic | Description                  |                                            |    |    |    |    |

| 7 - 0      | R9:2            | PLL Most Sig<br>8 MSB of the | <b>nificant Bits F</b><br>10-bit R divider |    |    |    |    |

Reset Value = 0000 0000b

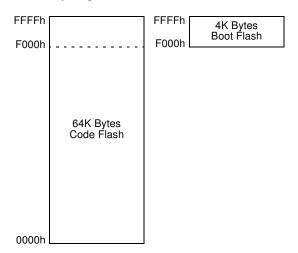

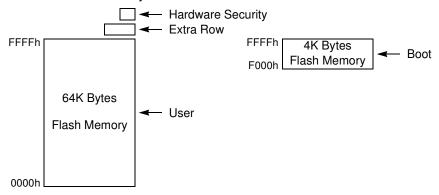

# 7. Program/Code Memory

The AT89C5132 implements 64K Bytes of on-chip program/code memory. Figure 7-1 shows the split of internal and external program/code memory spaces depending on the product.

The Flash memory increases EPROM and ROM functionality by in-circuit electrical erasure and programming. The high voltage needed for programming or erasing Flash cells is generated on-chip using the standard  $V_{DD}$  voltage, made possible by the internal charge pump. Thus, the AT89C5132 can be programmed using only one voltage and allows in application software programming. Hardware programming mode is also available using common programming tools. See the application note 'Programming T89C51x and AT89C51x with Device Programmers'.

The AT89C5132 implements an additional 4K Bytes of on-chip boot Flash memory provided in Flash memory. This boot memory is delivered programmed with a standard bootloader software allowing In-System Programming (ISP). It also contains some Application Programming Interfaces (API), allowing In Application Programming (IAP) by using user's own bootloader.

Figure 7-1. Program/Code Memory Organization

### 7.1 Flash Memory Architecture

As shown in Figure 7-2 the AT89C5132 Flash memory is composed of four spaces detailed in the following paragraphs.

Figure 7-2. AT89C5132 Memory Architecture

#### 7.1.1 User Space

This space is composed of a 64K Bytes Flash memory organized in 512 pages of 128 Bytes. It contains the user's application code. This space can be read or written by both software and hardware modes.

### 7.1.2 Boot Space

This space is composed of a 4K Bytes Flash memory. It contains the bootloader for In-System Programming and the routines for In-System Application Programming.

This space can only be read or written by hardware mode using a parallel programming tool.

#### 7.1.3 Hardware Security Space

This space is composed of one byte: the Hardware Security Byte (HSB see Table 7) divided in two separate nibbles see Table 7. The MSN contains the X2 mode configuration bit and the Boot Loader Jump Bit as detailed in section "Boot Memory Execution" and can be written by software while the LSN contains the lock system level to protect the memory content against piracy as detailed in section "Hardware Security System" and can only be written by hardware.

#### 7.1.4 Extra Row Space

This space is composed of two Bytes:

- The Software Boot Vector (SBV see Table 8).

This byte is used by the software bootloader to build the boot address.

- The Software Security Byte (SSB see Figure).

This byte is used to lock the execution of some bootloader commands.

### 7.2 Hardware Security System

The AT89C5132 implements three lock Bits LB2:0 in the LSN of HSB (see Table 7) providing three levels of security for user's program as described in Table 7 while the AT83C51SND1C is always set in read disabled mode.

- Level 0 is the level of an erased part and does not enable any security feature.

- Level 1 locks the hardware programming of both user and boot memories.

- Level 2 locks hardware verifying of both user and boot memories.

- Level 3 locks the external execution.

**Table 5.** Lock Bit Features<sup>(1)</sup>

| Level            | LB2 <sup>(2)</sup> | LB1 | LB0 | Internal<br>Execution | External<br>Execution | Hardware<br>Verifying | Hardware<br>Programming | Software<br>Programming |

|------------------|--------------------|-----|-----|-----------------------|-----------------------|-----------------------|-------------------------|-------------------------|

| 0                | U                  | U   | U   | Enable                | Enable                | Enable                | Enable                  | Enable                  |

| 1                | U                  | U   | Р   | Enable                | Enable                | Enable                | Disable                 | Enable                  |

| 2                | U                  | Р   | Х   | Enable                | Enable                | Disable               | Disable                 | Enable                  |

| 3 <sup>(3)</sup> | Р                  | Х   | Х   | Enable                | Disable               | Disable               | Disable                 | Enable                  |

Notes: 1. U means unprogrammed, P means programmed and X means don't care (programmed or unprogrammed).

- 2. LB2 is not implemented in the AT89C5132 products.

- 3. AT89C5132 products are delivered with third level programmed to ensure that the code programmed by software using ISP or user's bootloader is secured from any hardware piracy.

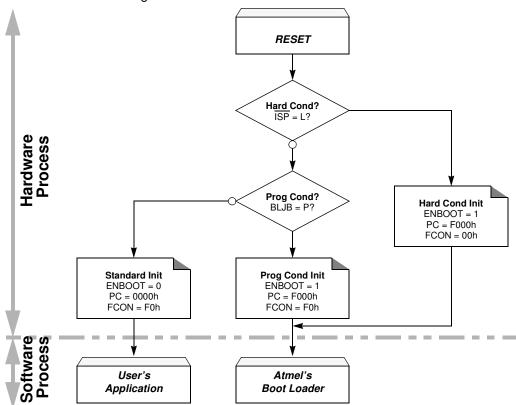

### 7.3 Boot Memory Execution

As internal C51 code space is limited to 64K Bytes, some mechanisms are implemented to allow boot memory to be mapped in the code space for execution at addresses from F000h to FFFFh. The boot memory is enabled by setting the ENBOOT bit in AUXR1 (see Table 6). The three ways to set this bit are detailed in the following sections.

#### 7.3.1 Software Boot Mapping

The software way to set ENBOOT consists in writing to AUXR1 from the user's software. This enables bootloader or API routines execution.

#### 7.3.2 Hardware Condition Boot Mapping

The hardware condition is based on the  $\overline{\text{ISP}}$  pin. When driving this pin to low level, the chip reset sets ENBOOT and forces the reset vector to F000h instead of 0000h in order to execute the bootloader software.

As shown in Figure 7-3, the hardware condition always allows in-system recovery when user's memory has been corrupted.

#### 7.3.3 Programmed Condition Boot Mapping

The programmed condition is based on the Bootloader Jump Bit (BLJB) in HSB. As shown in Figure 7-3, when this bit is programmed (by hardware or software programming mode), the chip resets ENBOOT and forces the reset vector to F000h instead of 0000h, in order to execute the bootloader software.

Figure 7-3. Hardware Boot Process Algorithm

The software process (bootloader) is detailed in the AT89C5132 Bootloader datasheet.

### 7.3.4 Preventing Flash Corruption

See "Reset Recommendation to Prevent Flash Corruption" on page 45.

# 7.4 Registers

**Table 6.** AUXR1 Register AUXR1 (S:A2h) – Auxiliary Register 1

| 7 | 6 | 5      | 4 | 3   | 2 | 1 | 0   |

|---|---|--------|---|-----|---|---|-----|

| - | - | ENBOOT | - | GF3 | 0 | - | DPS |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                       |

|------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 - 6      | -               | Reserved The values read from these Bits are indeterminate. Do not set these Bits.                                                                |

| 5          | ENBOOT          | Enable Boot Flash Set this bit to map the boot Flash in the code space between at addresses F000h to FFFFh. Clear this bit to disable boot Flash. |

| 4          | -               | Reserved The values read from this bit is indeterminate. Do not set this bit.                                                                     |

| 3          | GF3             | General Flag This bit is a general-purpose user flag.                                                                                             |

| 2          | 0               | Always Zero This bit is stuck to logic 0 to allow INC AUXR1 instruction without affecting GF3 flag.                                               |

| 1          | -               | Reserved for Data Pointer Extension.                                                                                                              |

| 0          | DPS             | Data Pointer Select Bit Set to select second data pointer: DPTR1. Clear to select first data pointer: DPTR0.                                      |

Reset Value = XXXX 00X0b

# 7.5 Hardware Bytes

Table 7. HSB Byte - Hardware Security Byte

| 7   | 6    | 5 | 4 | 3 | 2   | 1   | 0   |

|-----|------|---|---|---|-----|-----|-----|

| X2B | BLJB | - | - | - | LB2 | LB1 | LB0 |

| Bit Number | Bit<br>Mnemonic     | Description                                                                                                                                                                               |

|------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | X2B <sup>(1)</sup>  | X2 Bit Program this bit to start in X2 mode. Unprogram (erase) this bit to start in standard mode.                                                                                        |

| 6          | BLJB <sup>(2)</sup> | Boot Loader Jump Bit Program this bit to execute the boot loader at address F000h on next reset. Unprogram (erase) this bit to execute user's application at address 0000h on next reset. |

| 5 - 4      | -                   | Reserved The value read from these bits is always unprogrammed. Do not program these bits.                                                                                                |

| 3          | -                   | Reserved The value read from this bit is always unprogrammed. Do not program this bit.                                                                                                    |

| Bit Number | Bit<br>Mnemonic | Description                                       |

|------------|-----------------|---------------------------------------------------|

| 2 - 0      | LB2:0           | Hardware Lock Bits Refer to for bits description. |

Reset Value = XXUU UXXX, UUUU UUUU after an hardware full chip erase.

Note: 1. X2B initializes the X2 bit in CKCON during the reset phase.

- 2. In order to ensure boot loader activation at first power-up, AT89C5132 products are delivered with BLJB programmed.

- 3. Bits 0 to 3 (LSN) can only be programmed by hardware mode.

**Table 8.** SBV Byte – Software Boot Vector

| 7          | 6               | 5           | 4     | 3                                  | 2                               | 1              | 0       |

|------------|-----------------|-------------|-------|------------------------------------|---------------------------------|----------------|---------|

| ADD15      | ADD14           | ADD13       | ADD12 | ADD11                              | ADD10                           | ADD9           | ADD8    |

| Bit Number | Bit<br>Mnemonic | Description |       |                                    |                                 |                |         |

| 7 - 0      | ADD15:8         |             |       | ler 16-bit addr<br>sheet for usage | ess location<br>information (bo | otloader deper | ndent). |

Reset Value = XXXX XXXX, UUUU UUUU after an hardware full chip erase.

**Table 9.** SSB Byte – Software Security Byte

| 7          | 6               | 5                               | 4    | 3    | 2               | 1              | 0       |

|------------|-----------------|---------------------------------|------|------|-----------------|----------------|---------|

| SSB7       | SSB6            | SSB5                            | SSB4 | SSB3 | SSB2            | SSB1           | SSB0    |

| Bit Number | Bit<br>Mnemonic | Description                     |      |      |                 |                |         |

| 7 - 0      | SSB7:0          | Software Sec<br>Refer to the bo |      |      | information (bo | otloader deper | ndent). |

Reset Value = XXXX XXXX, UUUU UUUU after an hardware full chip erase.

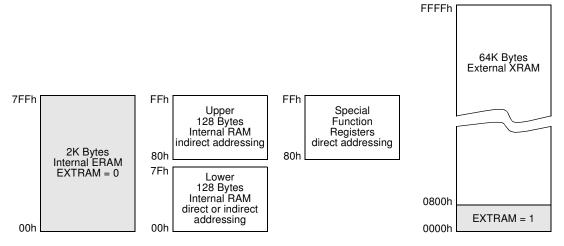

# 8. Data Memory

The AT89C5132 provides data memory access in two different spaces:

- The internal space mapped in three separate segments:

- The lower 128 Bytes RAM segment

- The upper 128 Bytes RAM segment

- The expanded 2048 Bytes RAM segment

- 2. The external space.

A fourth internal segment is available but dedicated to Special Function Registers, SFRs, (addresses 80h to FFh) accessible by direct addressing mode. For information on this segment, refer to the section "Special Function Registers", page 29.

Figure 8-1 shows the internal and external data memory spaces organization.

Figure 8-1. Internal and External Data Memory Organization

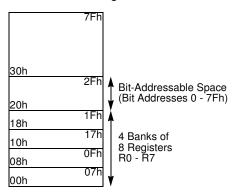

### 8.1 Internal Space

#### 8.1.1 Lower 128 Bytes RAM

The lower 128 Bytes of RAM (see Figure 8-2) are accessible from address 00h to 7Fh using direct or indirect addressing modes. The lowest 32 Bytes are grouped into 4 banks of 8 registers (R0 to R7). Two Bits RS0 and RS1 in PSW register (see Table 13) select which bank is in use according to Table 10. This allows more efficient use of code space, since register instructions are shorter than instructions that use direct addressing, and can be used for context switching in interrupt service routines.

**Table 10.** Register Bank Selection

| RS1 | RS0 | Description                     |

|-----|-----|---------------------------------|

| 0   | 0   | Register bank 0 from 00h to 07h |

| 0   | 1   | Register bank 1 from 08h to 0Fh |

| 1   | 0   | Register bank 2 from 10h to 17h |

| 1   | 1   | Register bank 3 from 18h to 1Fh |

The next 16 Bytes above the register banks form a block of bit-addressable memory space. The C51 instruction set includes a wide selection of single-bit instructions, and the 128 Bits in this area can be directly addressed by these instructions. The bit addresses in this area are 00h to 7Fh.

Figure 8-2. Lower 128 Bytes Internal RAM Organization

#### 8.1.2 Upper 128 Bytes RAM

The upper 128 Bytes of RAM are accessible from address 80h to FFh using only indirect addressing mode.

#### 8.1.3 Expanded RAM

The on-chip 2K Bytes of expanded RAM (ERAM) are accessible from address 0000h to 07FFh using indirect addressing mode through MOVX instructions. In this address range, EXTRAM bit in AUXR register (see Table 14) is used to select the ERAM (default) or the XRAM. As shown in Figure 8-1 when EXTRAM = 0, the ERAM is selected and when EXTRAM = 1, the XRAM is selected, See "External Space" on page 23.

The ERAM memory can be resized using XRS1:0 Bits in AUXR register to dynamically increase external access to the XRAM space. Table 11 details the selected ERAM size and address range.

Table 11. ERAM Size Selection

| XRS1 | XRS0 | ERAM Size | Address    |

|------|------|-----------|------------|

| 0    | 0    | 256 Bytes | 0 to 00FFh |

| 0    | 1    | 512 Bytes | 0 to 01FFh |

| 1    | 0    | 1K Byte   | 0 to 03FFh |

| 1    | 1    | 2K Bytes  | 0 to 07FFh |

Note: Lower 128 Bytes RAM, Upper 128 Bytes RAM, and expanded RAM are made of volatile memory cells. This means that the RAM content is indeterminate after power-up and must then be initialized properly.

### 8.2 External Space

#### 8.2.1 Memory Interface

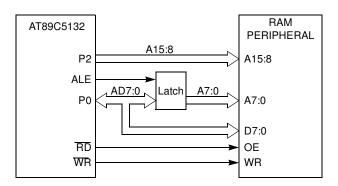

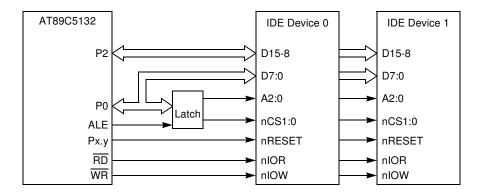

The external memory interface comprises the external bus (port 0 and port 2) as well as the bus control signals ( $\overline{RD}$ ,  $\overline{WR}$ , and ALE).

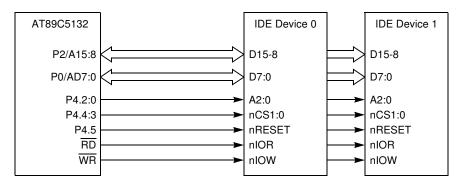

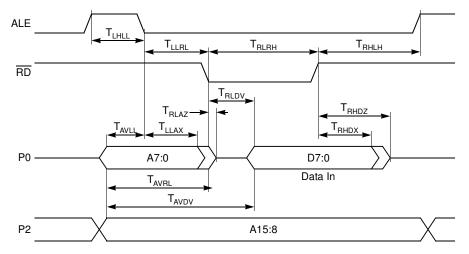

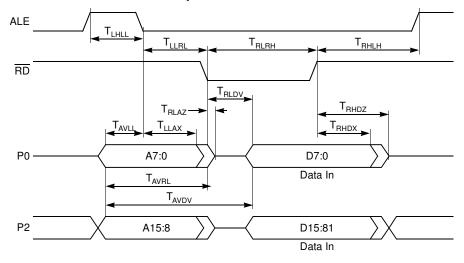

Figure 8-3 shows the structure of the external address bus. P0 carries address A7:0 while P2 carries address A15:8. Data D7:0 is multiplexed with A7:0 on P0. Table 12 describes the external memory interface signals.

Figure 8-3. External Data Memory Interface Structure

Table 12. External Data Memory Interface Signals

| Signal<br>Name | Туре | Description                                                                                             | Alternate<br>Function |

|----------------|------|---------------------------------------------------------------------------------------------------------|-----------------------|

| A15:8          | 0    | Address Lines Upper address lines for the external bus.                                                 | P2.7:0                |

| AD7:0          | I/O  | Address/Data Lines Multiplexed lower address lines and data for the external memory.                    | P0.7:0                |

| ALE            | 0    | Address Latch Enable ALE signals indicates that valid address information are available on lines AD7:0. | -                     |

| RD             | 0    | Read Read signal output to external data memory.                                                        | P3.7                  |

| WR             | 0    | Write Write signal output to external memory.                                                           | P3.6                  |

#### 8.2.2 Page Access Mode

The AT89C5132 implement a feature called Page Access that disables the output of DPH on P2 when executing MOVX @DPTR instruction. Page Access is enable by setting the DPHDIS bit in AUXR register.

Page Access is useful when application uses both ERAM and 256 Bytes of XRAM. In this case, software modifies intensively EXTRAM bit to select access to ERAM or XRAM and must save it if used in interrupt service routine. Page Access allows external access above 00FFh address without generating DPH on P2. Thus ERAM is accessed using MOVX @Ri or MOVX @DPTR with DPTR < 0100h, < 0200h, < 0400h or < 0800h depending on the XRS1:0 bits value. Then XRAM is accessed using MOVX @DPTR with DPTR ≥ 0800h regardless of XRS1:0 bits value while keeping P2 for general I/O usage.

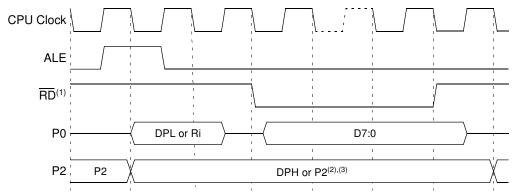

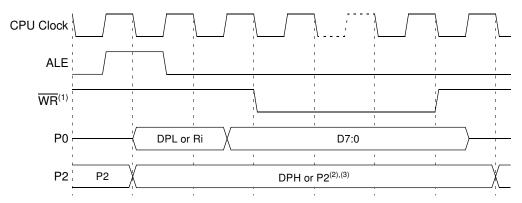

#### 8.2.3 External Bus Cycles

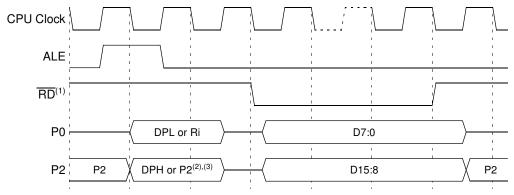

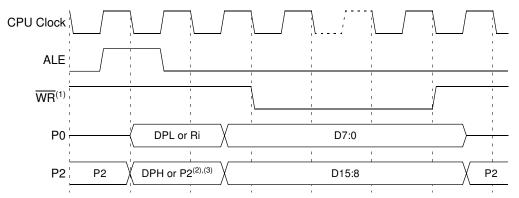

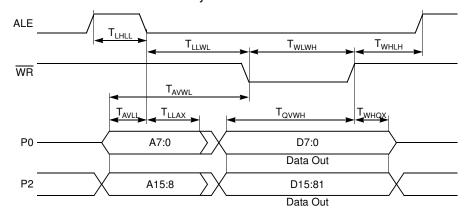

This section describes the bus cycles that AT89C5132 executes to read (see Figure 8-4), and write data (see Figure 8-5) in the external data memory.

External memory cycle takes 6 CPU clock periods. This is equivalent to 12 oscillator clock periods in standard mode or 6 oscillator clock periods in X2 mode. For further information on X2 mode, refer to the section "X2 Feature", page 12.

Slow peripherals can be accessed by stretching the read and write cycles. This is done using the M0 bit in AUXR register. Setting this bit changes the width of the RD and WR signals from 3 to 15 CPU clock periods.

For simplicity, the accompanying figures depict the bus cycle waveforms in idealized form and do not provide precise timing information. For bus cycle timing parameters refer to the section "AC Characteristics".

Figure 8-4. External Data Read Waveforms

Notes: 1. RD signal may be stretched using M0 bit in AUXR register.

- 2. When executing MOVX @Ri instruction, P2 outputs SFR content.

- 3. When executing MOVX @DPTR instruction, if DPHDIS is set (Page Access Mode), P2 outputs SFR content instead of DPH.

Figure 8-5. External Data Write Waveforms

Notes: 1. WR signal may be stretched using M0 bit in AUXR register.

- 2. When executing MOVX @Ri instruction, P2 outputs SFR content.

- When executing MOVX @DPTR instruction, if DPHDIS is set (Page Access Mode), P2 outputs SFR content instead of DPH.

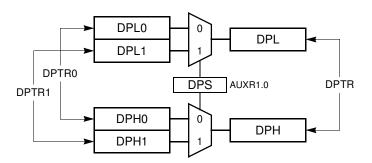

#### 8.3 Dual Data Pointer

#### 8.3.1 Description

The AT89C5132 implement a second data pointer for speeding up code execution and reducing code size in case of intensive usage of external memory accesses.

DPTR0 and DPTR1 are seen by the CPU as DPTR and are accessed using the SFR addresses 83h and 84h that are the DPH and DPL addresses. The DPS bit in AUXR1 register (see Table 15) is used to select whether DPTR is the data pointer 0 or the data pointer 1 (see Figure 8-6).

Figure 8-6. Dual Data Pointer Implementation

#### 8.3.2 Application

Software can take advantage of the additional data pointers to both increase speed and reduce code size, for example, block operations (copy, compare, search ...) are well served by using one data pointer as a "source" pointer and the other one as a "destination" pointer.

Below is an example of block move implementation using the two pointers and coded in assembler. The latest C compiler also takes advantage of this feature by providing enhanced algorithm libraries.

The INC instruction is a short (2 Bytes) and fast (6 CPU clocks) way to manipulate the DPS bit in the AUXR1 register. However, note that the INC instruction does not directly forces the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is "0" or "1" on entry.

```

; ASCII block move using dual data pointers

; Modifies DPTRO, DPTR1, A and PSW

; Ends when encountering NULL character

; Note: DPS exits opposite of entry state unless an extra INC AUXR1 is added

AUXR1

0A2h

EOU

move:

mov

DPTR, #SOURCE ; address of SOURCE

; switch data pointers

inc

AUXR1

mov

DPTR, #DEST

; address of DEST

mv_loop: inc

AUXR1

; switch data pointers

A,@DPTR

; get a byte from SOURCE

movx

DPTR

; increment SOURCE address

inc

inc

AUXR1

; switch data pointers

movx

@DPTR,A

; write the byte to DEST

inc

DPTR

; increment DEST address

mv_loop

: check for NULL terminator

inz

end_move:

```

# 8.4 Registers

**Table 13.** PSW Register PSW (S:8Eh) – Program Status Word Register

| 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----|----|----|-----|-----|----|----|---|

| CY | AC | F0 | RS1 | RS0 | ov | F1 | Р |

| Bit Number | Bit<br>Mnemonic | Description                                                                                             |

|------------|-----------------|---------------------------------------------------------------------------------------------------------|

| 7          | CY              | Carry Flag Carry out from bit 1 of ALU operands.                                                        |

| 6          | AC              | Auxiliary Carry Flag Carry out from bit 1 of addition operands.                                         |

| 5          | F0              | User Definable Flag 0.                                                                                  |

| 4 - 3      | RS1:0           | Register Bank Select Bits Refer to Table 10 for Bits description.                                       |

| 2          | OV              | Overflow Flag Overflow set by arithmetic operations.                                                    |

| 1          | F1              | User Definable Flag 1                                                                                   |

| 0          | Р               | Parity Bit Set when ACC contains an odd number of 1's. Cleared when ACC contains an even number of 1's. |

Reset Value = 0000 0000b

Table 14. AUXR Register

AUXR (S:8Eh) - Auxiliary Control Register

| 7 | 6     | 5  | 4      | 3    | 2    | 1      | 0  |

|---|-------|----|--------|------|------|--------|----|

| - | EXT16 | МО | DPHDIS | XRS1 | XRS0 | EXTRAM | AO |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                                                                      |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | -               | Reserved The values read from this bit is indeterminate. Do not set this bit.                                                                                                                    |

| 6          | EXT16           | External 16-bit Access Enable Bit Set to enable 16-bit access mode during MOVX instructions. Clear to disable 16-bit access mode and enable standard 8-bit access mode during MOVX instructions. |

| 5          | M0              | External Memory Access Stretch Bit Set to stretch RD or WR signals duration to 15 CPU clock periods. Clear not to stretch RD or WR signals and set duration to 3 CPU clock periods.              |

| 4          | DPHDIS          | DPH Disable Bit Set to disable DPH output on P2 when executing MOVX @DPTR instruction. Clear to enable DPH output on P2 when executing MOVX @DPTR instruction.                                   |

| 3 - 2      | XRS1:0          | Expanded RAM Size Bits Refer to Table 11 for ERAM size description.                                                                                                                              |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                                                                               |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | EXTRAM          | External RAM Enable Bit Set to select the external XRAM when executing MOVX @Ri or MOVX @DPTR instructions. Clear to select the internal expanded RAM when executing MOVX @Ri or MOVX @DPTR instructions. |

| 0          | AO              | ALE Output Enable Bit Set to output the ALE signal only during MOVX instructions. Clear to output the ALE signal at a constant rate of F <sub>CPU</sub> /3.                                               |

Reset Value = X000 1101b

# 9. Special Function Registers

The Special Function Registers (SFRs) of the AT89C5132 derivatives fall into the categories detailed in Table 15 to Table 30. The relative addresses of these SFRs are provided together with their reset values in Table 31. In this table, the bit-addressable registers are identified by Note 1.

Table 15. C51 Core SFRs

| Mnemonic | Add | Name                   | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----------|-----|------------------------|----|----|----|-----|-----|----|----|---|

| ACC      | E0h | Accumulator            |    |    |    |     |     |    |    |   |

| В        | F0h | B Register             |    |    |    |     |     |    |    |   |

| PSW      | D0h | Program Status Word    | CY | AC | F0 | RS1 | RS0 | OV | F1 | Р |

| SP       | 81h | Stack Pointer          |    |    |    |     |     |    |    |   |

| DPL      | 82h | Data Pointer Low byte  |    |    |    |     |     |    |    |   |

| DPH      | 83h | Data Pointer High byte |    |    |    |     |     |    |    |   |

Table 16. System Management SFRs

| Mnemonic | Add | Name                 | 7     | 6     | 5      | 4      | 3    | 2    | 1      | 0   |

|----------|-----|----------------------|-------|-------|--------|--------|------|------|--------|-----|

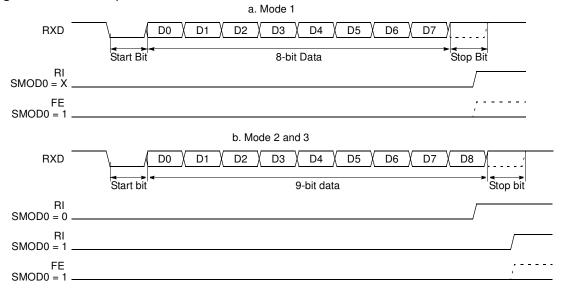

| PCON     | 87h | Power Control        | SMOD1 | SMOD0 | -      | -      | GF1  | GF0  | PD     | IDL |

| AUXR     | 8Eh | Auxiliary Register 0 | -     | EXT16 | MO     | DPHDIS | XRS1 | XRS0 | EXTRAM | AO  |

| AUXR1    | A2h | Auxiliary Register 1 | -     | -     | ENBOOT | -      | GF3  | 0    | -      | DPS |

| NVERS    | FBh | Version Number       | NV7   | NV6   | NV5    | NV4    | NV3  | NV2  | NV1    | NV0 |

Table 17. PLL and System Clock SFRs

| Mnemonic | Add | Name          | 7  | 6    | 5  | 4  | 3      | 2    | 1     | 0     |

|----------|-----|---------------|----|------|----|----|--------|------|-------|-------|

| CKCON    | 8Fh | Clock Control | -  | WDX2 | -  | -  | -      | T1X2 | T0X2  | X2    |

| PLLCON   | E9h | PLL Control   | R1 | R0   | -  | -  | PLLRES | -    | PLLEN | PLOCK |

| PLLNDIV  | EEh | PLL N Divider | -  | N6   | N5 | N4 | N3     | N2   | N1    | N0    |

| PLLRDIV  | EFh | PLL R Divider | R9 | R8   | R7 | R6 | R5     | R4   | R3    | R2    |

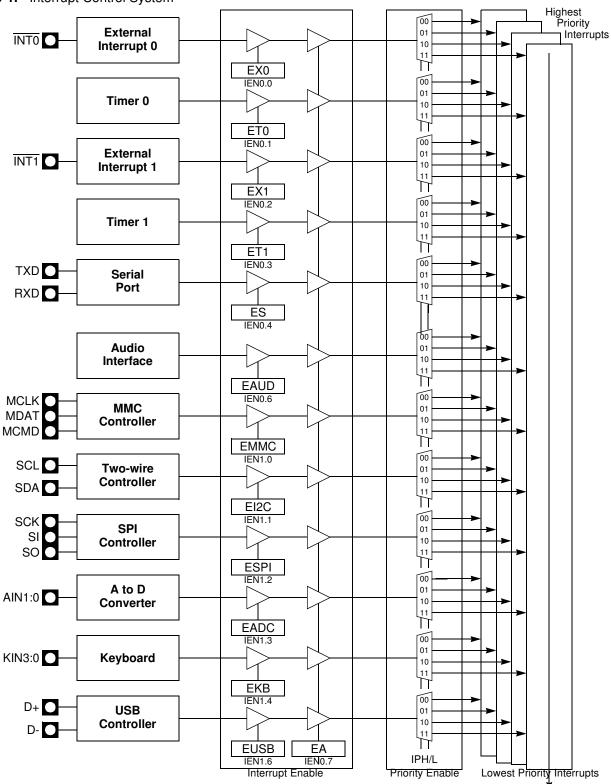

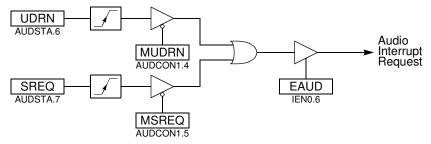

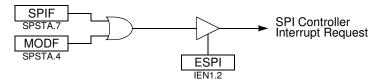

Table 18. Interrupt SFRs

| Mnemonic | Add | Name                              | 7  | 6      | 5 | 4     | 3      | 2      | 1      | 0      |

|----------|-----|-----------------------------------|----|--------|---|-------|--------|--------|--------|--------|

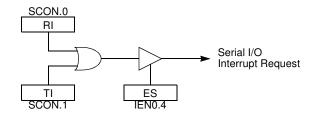

| IEN0     | A8h | Interrupt Enable Control 0        | EA | EAUD   | - | ES    | ET1    | EX1    | ET0    | EX0    |

| IEN1     | B1h | Interrupt Enable Control 1        | -  | EUSB   | - | EKB   | EADC   | ESPI   | EI2C   | EMMC   |

| IPH0     | B7h | Interrupt Priority Control High 0 | -  | IPHAUD | - | IPHS  | IPHT1  | IPHX1  | IPHT0  | IPHX0  |

| IPL0     | B8h | Interrupt Priority Control Low 0  | -  | IPLAUD | - | IPLS  | IPLT1  | IPLX1  | IPLT0  | IPLX0  |

| IPH1     | B3h | Interrupt Priority Control High 1 | -  | IPHUSB | - | IPHKB | IPHADC | IPHSPI | IPHI2C | IPHMMC |

| IPL1     | B2h | Interrupt Priority Control Low 1  | -  | IPLUSB | - | IPLKB | IPLADC | IPLSPI | IPLI2C | IPLMMC |

Table 19. Port SFRs

| Mnemonic | Add | Name         | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-----|--------------|---|---|---|---|---|---|---|---|

| P0       | 80h | 8-bit Port 0 |   |   |   |   |   |   |   |   |

| P1       | 90h | 8-bit Port 1 |   |   |   |   |   |   |   |   |

| P2       | A0h | 8-bit Port 2 |   |   |   |   |   |   |   |   |

| P3       | B0h | 8-bit Port 3 |   |   |   |   |   |   |   |   |

| P4       | C0h | 8-bit Port 4 |   |   |   |   |   |   |   |   |

| P5       | D8h | 4-bit Port 5 | - | - | - | - |   |   |   |   |

# Table 20. Flash Memory SFR

| Mnemonic | Add | Name          | 7    | 6    | 5    | 4    | 3   | 2     | 1     | 0     |

|----------|-----|---------------|------|------|------|------|-----|-------|-------|-------|

| FCON     | D1h | Flash Control | FPL3 | FPL2 | FPL1 | FPL0 | FPS | FMOD1 | FMOD0 | FBUSY |

### Table 21. Timer SFRs

| Mnemonic | Add | Name                          | 7     | 6     | 5   | 4   | 3     | 2     | 1    | 0    |

|----------|-----|-------------------------------|-------|-------|-----|-----|-------|-------|------|------|

| TCON     | 88h | Timer/Counter 0 and 1 Control | TF1   | TR1   | TF0 | TR0 | IE1   | IT1   | IE0  | IT0  |

| TMOD     | 89h | Timer/Counter 0 and 1 Modes   | GATE1 | C/T1# | M11 | M01 | GATE0 | C/T0# | M10  | M00  |

| TL0      | 8Ah | Timer/Counter 0 Low Byte      |       |       |     |     |       |       |      |      |

| TH0      | 8Ch | Timer/Counter 0 High Byte     |       |       |     |     |       |       |      |      |

| TL1      | 8Bh | Timer/Counter 1 Low Byte      |       |       |     |     |       |       |      |      |

| TH1      | 8Dh | Timer/Counter 1 High Byte     |       |       |     |     |       |       |      |      |

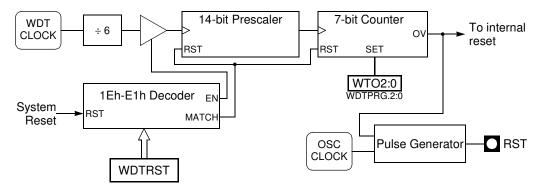

| WDTRST   | A6h | WatchDog Timer Reset          |       |       |     |     |       |       |      |      |

| WDTPRG   | A7h | WatchDog Timer Program        | =     | -     | -   | -   | -     | WTO2  | WTO1 | WTO0 |

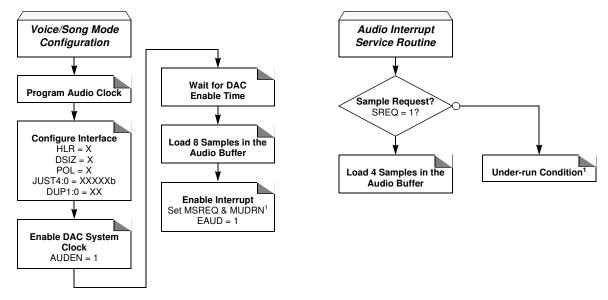

### Table 22. Audio Interface SFRs

| Mnemonic | Add | Name                | 7     | 6     | 5      | 4     | 3     | 2     | 1     | 0     |

|----------|-----|---------------------|-------|-------|--------|-------|-------|-------|-------|-------|

| AUDCON0  | 9Ah | Audio Control 0     | JUST4 | JUST3 | JUST2  | JUST1 | JUST0 | POL   | DSIZ  | HLR   |

| AUDCON1  | 9Bh | Audio Control 1     | SRC   | DRQEN | MSREQ  | MUDRN | -     | DUP1  | DUP0  | AUDEN |

| AUDSTA   | 9Ch | Audio Status        | SREQ  | UDRN  | AUBUSY | -     | -     | -     | -     | -     |

| AUDDAT   | 9Dh | Audio Data          | AUD7  | AUD6  | AUD5   | AUD4  | AUD3  | AUD2  | AUD1  | AUD0  |

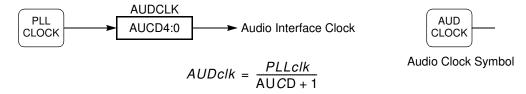

| AUDCLK   | ECh | Audio Clock Divider | -     | -     | -      | AUCD4 | AUCD3 | AUCD2 | AUCD1 | AUCD0 |

Table 23. USB Controller SFRs

| Mnemonic | Add | Name                          | 7     | 6           | 5           | 4       | 3       | 2           | 1       | 0       |

|----------|-----|-------------------------------|-------|-------------|-------------|---------|---------|-------------|---------|---------|

| USBCON   | BCh | USB Global Control            | USBE  | SUSPCL<br>K | SDRMWU<br>P | -       | UPRSM   | RMWUPE      | CONFG   | FADDEN  |

| USBADDR  | C6h | USB Address                   | FEN   | UADD6       | UADD5       | UADD4   | UADD3   | UADD2       | UADD1   | UADD0   |

| USBINT   | BDh | USB Global Interrupt          | -     | -           | WUPCPU      | EORINT  | SOFINT  | -           | -       | SPINT   |

| USBIEN   | BEh | USB Global Interrupt Enable   | -     | -           | EWUPCP<br>U | EEORINT | ESOFINT | -           | -       | ESPINT  |

| UEPNUM   | C7h | USB Endpoint Number           | -     | -           | -           | -       | -       | -           | EPNUM1  | EPNUM0  |

| UEPCONX  | D4h | USB Endpoint X Control        | EPEN  | -           | -           | -       | DTGL    | EPDIR       | EPTYPE1 | EPTYPE0 |

| UEPSTAX  | CEh | USB Endpoint X Status         | DIR   | -           | STALLRQ     | TXRDY   | STLCRC  | RXSETU<br>P | RXOUT   | TXCMP   |

| UEPRST   | D5h | USB Endpoint Reset            | -     | -           | -           | -       | EP3RST  | EP2RST      | EP1RST  | EP0RST  |

| UEPINT   | F8h | USB Endpoint Interrupt        | -     | -           | -           | -       | EP3INT  | EP2INT      | EP1INT  | EP0INT  |

| UEPIEN   | C2h | USB Endpoint Interrupt Enable | -     | -           | -           | -       | EP3INTE | EP2INTE     | EP1INTE | EP0INTE |

| UEPDATX  | CFh | USB Endpoint X FIFO Data      | FDAT7 | FDAT6       | FDAT5       | FDAT4   | FDAT3   | FDAT2       | FDAT1   | FDAT0   |

| UBYCTX   | E2h | USB Endpoint X Byte Counter   | _     | ВҮСТ6       | BYCT5       | BYCT4   | ВҮСТ3   | BYCT2       | BYCT1   | BYCT0   |

| UFNUML   | BAh | USB Frame Number Low          | FNUM7 | FNUM6       | FNUM5       | FNUM4   | FNUM3   | FNUM2       | FNUM1   | FNUM0   |

| UFNUMH   | BBh | USB Frame Number High         | -     | -           | CRCOK       | CRCERR  | -       | FNUM10      | FNUM9   | FNUM8   |

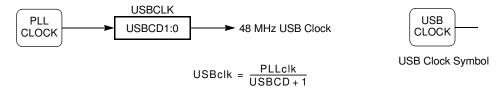

| USBCLK   | EAh | USB Clock Divider             | -     | -           | -           | -       | =       | -           | USBCD1  | USBCD0  |

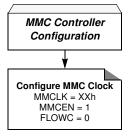

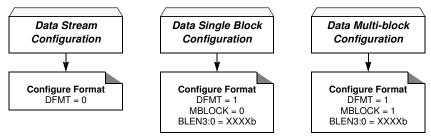

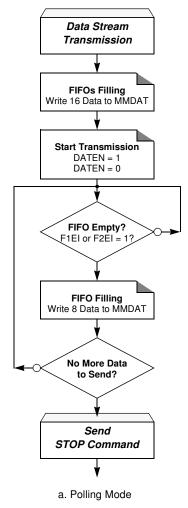

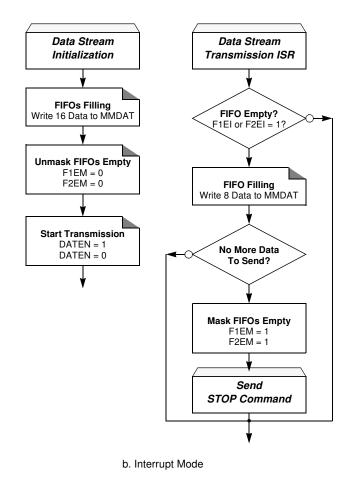

### Table 24. MMC Controller SFRs

| Mnemonic | Add | Name                   | 7     | 6     | 5     | 4      | 3      | 2     | 1      | 0      |

|----------|-----|------------------------|-------|-------|-------|--------|--------|-------|--------|--------|

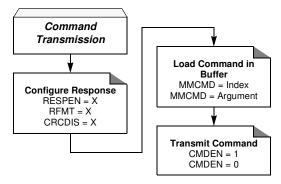

| MMCON0   | E4h | MMC Control 0          | DRPTR | DTPTR | CRPTR | CTPTR  | MBLOCK | DFMT  | RFMT   | CRCDIS |

| MMCON1   | E5h | MMC Control 1          | BLEN3 | BLEN2 | BLEN1 | BLEN0  | DATDIR | DATEN | RESPEN | CMDEN  |

| MMCON2   | E6h | MMC Control 2          | MMCEN | DCR   | CCR   | -      | -      | DATD1 | DATD0  | FLOWC  |

| MMSTA    | DEh | MMC Control and Status | -     | -     | CBUSY | CRC16S | DATFS  | CRC7S | RESPFS | CFLCK  |

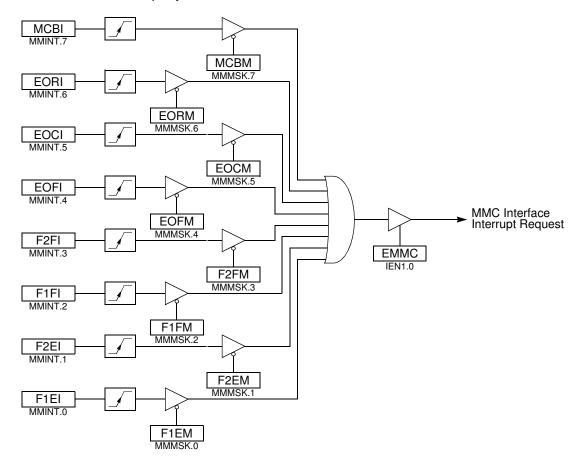

| MMINT    | E7h | MMC Interrupt          | MCBI  | EORI  | EOCI  | EOFI   | F2FI   | F1FI  | F2EI   | F1EI   |

| MMMSK    | DFh | MMC Interrupt Mask     | MCBM  | EORM  | EOCM  | EOFM   | F2FM   | F1FM  | F2EM   | F1EM   |

| MMCMD    | DDh | MMC Command            | MC7   | MC6   | MC5   | MC4    | МС3    | MC2   | MC1    | MC0    |

| MMDAT    | DCh | MMC Data               | MD7   | MD6   | MD5   | MD4    | MD3    | MD2   | MD1    | MD0    |

| MMCLK    | EDh | MMC Clock Divider      | MMCD7 | MMCD6 | MMCD5 | MMCD4  | MMCD3  | MMCD2 | MMCD1  | MMCD0  |

# Table 25. IDE Interface SFR

| Mnemonic | Add | Name                 | 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

|----------|-----|----------------------|-----|-----|-----|-----|-----|-----|----|----|

| DAT16H   | F9h | High Order Data Byte | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 |

Table 26. Serial I/O Port SFRs

| Mnemonic | Add | Name               | 7      | 6   | 5   | 4   | 3    | 2    | 1   | 0   |

|----------|-----|--------------------|--------|-----|-----|-----|------|------|-----|-----|

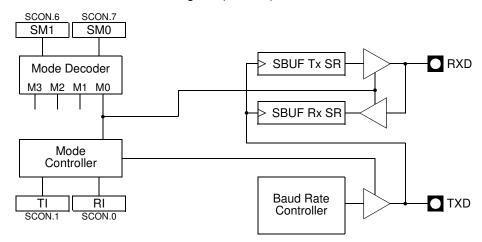

| SCON     | 98h | Serial Control     | FE/SM0 | SM1 | SM2 | REN | TB8  | RB8  | TI  | RI  |

| SBUF     | 99h | Serial Data Buffer |        |     |     |     |      |      |     |     |

| SADEN    | B9h | Slave Address Mask |        |     |     |     |      |      |     |     |

| SADDR    | A9h | Slave Address      |        |     |     |     |      |      |     |     |

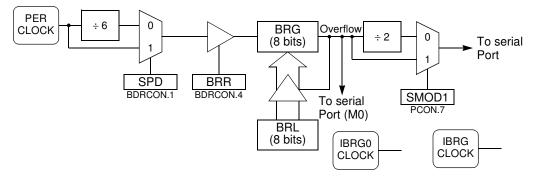

| BDRCON   | 92h | Baud Rate Control  | -      | -   | -   | BRR | TBCK | RBCK | SPD | SRC |

| BRL      | 91h | Baud Rate Reload   |        |     |     |     |      |      |     |     |

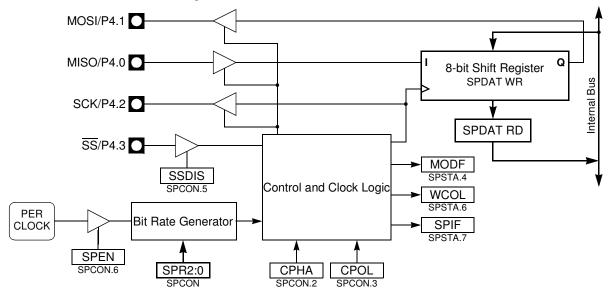

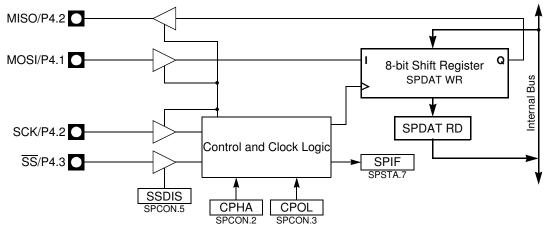

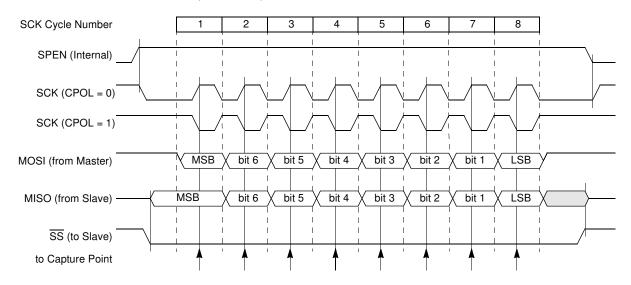

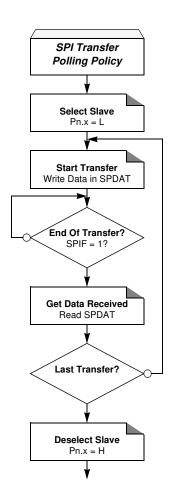

### Table 27. SPI Controller SFRs

| Mnemonic | Add | Name        | 7    | 6    | 5     | 4    | 3    | 2    | 1    | 0    |

|----------|-----|-------------|------|------|-------|------|------|------|------|------|

| SPCON    | C3h | SPI Control | SPR2 | SPEN | SSDIS | MSTR | CPOL | СРНА | SPR1 | SPR0 |

| SPSTA    | C4h | SPI Status  | SPIF | WCOL | -     | MODF | -    | -    | -    | -    |

| SPDAT    | C5h | SPI Data    | SPD7 | SPD6 | SPD5  | SPD4 | SPD3 | SPD2 | SPD1 | SPD0 |

### Table 28. Special Register

| Mnemonic | Add | Name     | 7     | 6    | 5     | 4     | 3    | 2    | 1     | 0     |

|----------|-----|----------|-------|------|-------|-------|------|------|-------|-------|

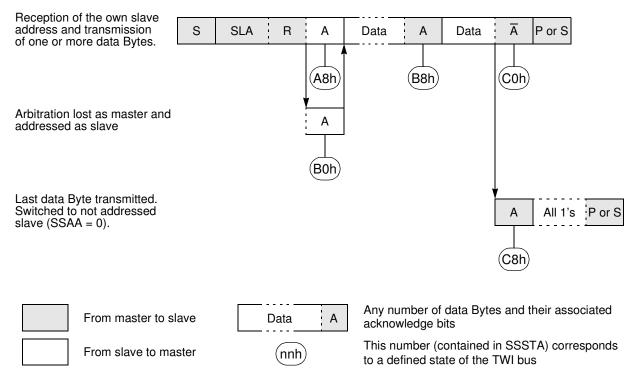

| SSCON    | 93h | Reserved | SSCR2 | SSPE | SSSTA | SSSTO | SSI  | SSAA | SSCR1 | SSCR0 |

| SSSTA    | 94h | Reserved | SSC4  | SSC3 | SSC2  | SSC1  | SSC0 | 0    | 0     | 0     |

| SSDAT    | 95h | Reserved | SSD7  | SSD6 | SSD5  | SSD4  | SSD3 | SSD2 | SSD1  | SSD0  |

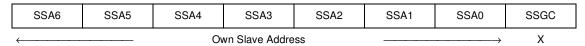

| SSADR    | 96h | Reserved | SSA7  | SSA6 | SSA5  | SSA4  | SSA3 | SSA2 | SSA1  | SSGC  |

# Table 29. Keyboard Interface SFRs

| Mnemonic | Add | Name             | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----------|-----|------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| KBCON    | A3h | Keyboard Control | KINL3 | KINL2 | KINL1 | KINL0 | KINM3 | KINM2 | KINM1 | KINM0 |

| KBSTA    | A4h | Keyboard Status  | KPDE  | -     | -     | -     | KINF3 | KINF2 | KINF1 | KINF0 |

# Table 30. A/D Controller SFRs

| Mnemonic | Add | Name               | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----------|-----|--------------------|-------|-------|-------|-------|-------|-------|-------|-------|

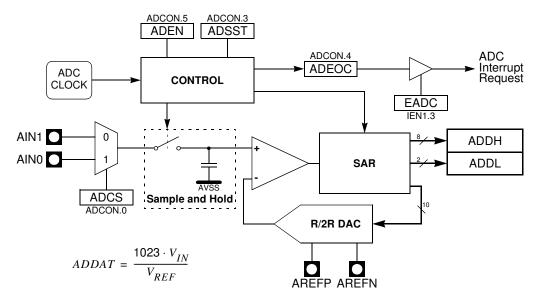

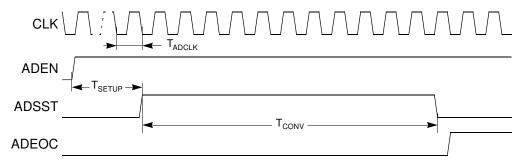

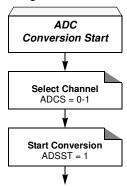

| ADCON    | F3h | ADC Control        | -     | ADIDL | ADEN  | ADEOC | ADSST | -     | -     | ADCS  |

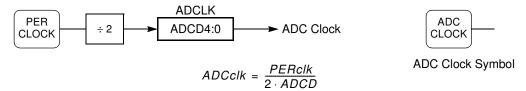

| ADCLK    | F2h | ADC Clock Divider  | -     | -     | -     | ADCD4 | ADCD3 | ADCD2 | ADCD1 | ADCD0 |

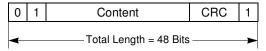

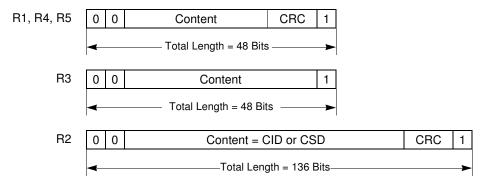

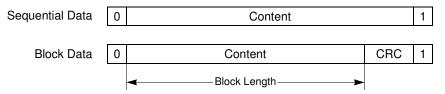

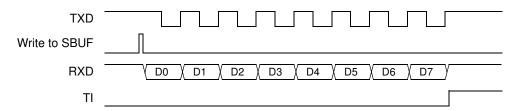

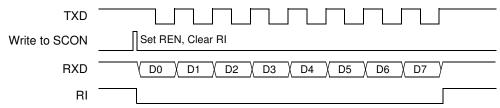

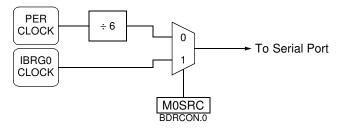

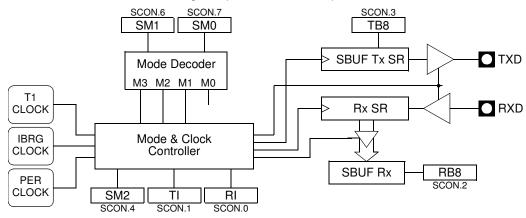

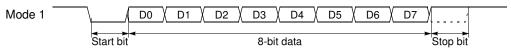

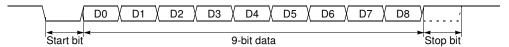

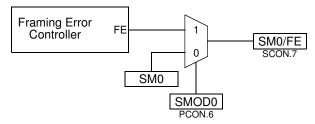

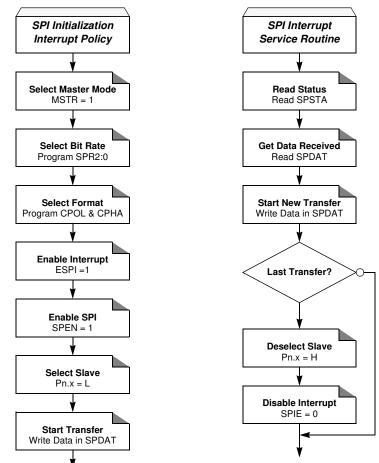

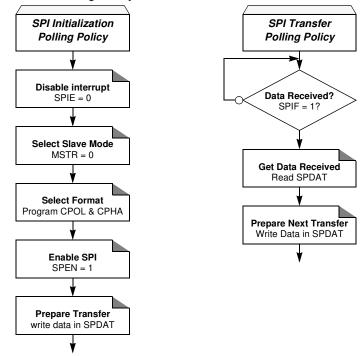

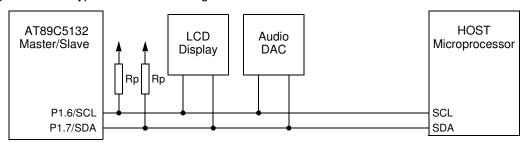

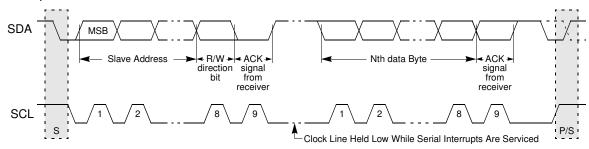

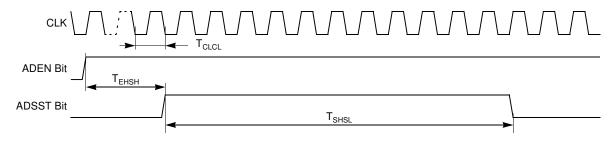

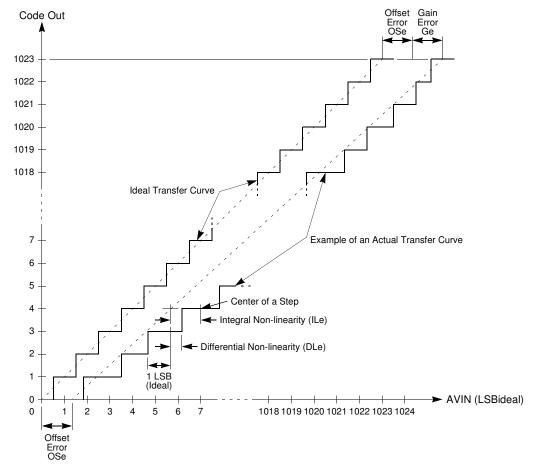

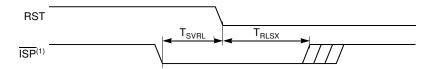

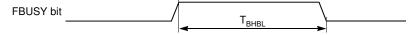

| ADDL     | F4h | ADC Data Low Byte  | -     | -     | -     | -     | -     | -     | ADAT1 | ADAT0 |